About

Brainiac’s Purpose

Brainiac is a tool to enable deeper understanding and new research into how the brain works and learns, possibly leading to human-like AI, Artificial General Intelligence (AGI). Brainiac clearly illustrates how, when and why neurons interact. As a tool, Brainiac was designed to serve teachers and researchers. And because it’s open-source, it can also serve software developers and coding instructors.

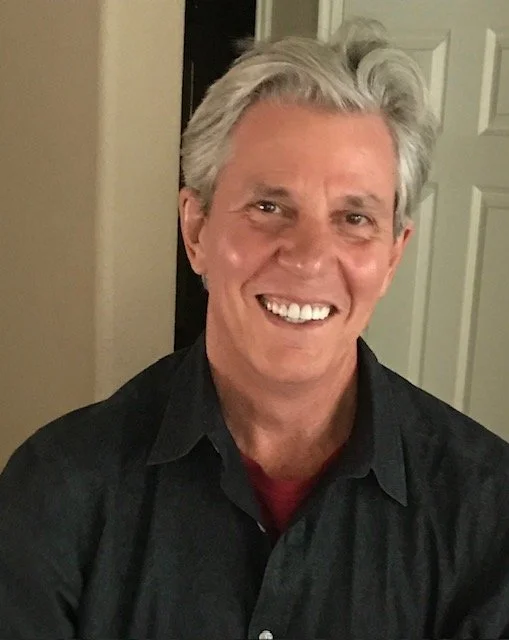

Founder – Paul Kollaritsch

Throughout his career as a software architect, Paul Kollaritsch has solved huge problems in the electronic chip world that involve architecting billions of transistors. Upon retirement, as a way of giving back to the community, he decided to use his “big picture” coding skills to singlehandedly create the first version of Brainiac.

After creating numerous patented software solutions, Paul consciously chose to make Brainiac open source. His intention is to spark the kind of “magical” creativity and breakthroughs that happen when eager contributors collaborate and build on one another’s work.

Since the start of his career, Paul has been on the leading edge of artificial intelligence (AI) research and application. As a researcher at Bell Laboratories in the early ’80s, Paul was one of the first people to apply AI to electronic chip design. He actually published the first papers on the subject, one of which earned Best Paper at the IEEE Custom Integrated Circuits Conference.

Through his later work at Cadence Design Systems, Paul solved complicated problems for QualComm, Apple, Cisco, Samsung, Sony, NVidia and many other leading tech companies.

In addition to holding 6 patents, Paul has had 7 papers published in highly respected journals (including 2 Best Papers), as well as a section in the go-to textbook on very large scale integrated-circuit (VLSI) design.

Career Highlights Include:

Served on DARPA Design Automation steering committee

Patent 4433331: Programmable logic array interconnection matrix, fundamental patent for FPGAs

BEST PAPER: AI expert systems applied to chip design. “Cadre – A system of cooperating VLSI design experts,” B. Ackland, P.W. Kollaritsch, et al., International Conference on Computer Design (ICCD). pp. 99-104 1985.

Patent 8707228: Method and system for implementing hierarchical prototyping of electronic designs, FlexModel invention

AWARD: Production Innovation Award for FlexModel technology in Encounter Digital Implementation System, Cadence Design Systems 2011

BEST PAPER: “Plan to Success: Fast Big Chip Hierarchical Floorplan,” M. Spohr, P. Kollaritsch, cdnLIVE EMEA 2010

Patent 9760667: Method, system, and computer program product for implementing prototyping and floorplanning of electronic circuit designs

Patent 8719743: Method and system for implementing clock tree prototyping

Patent 10540470: Generating a power grid for an integrated circuit

Patent 10242145: Optimizing a power grid for an integrated circuit

Textbook section, Principles of CMOS VLSI design: a systems perspective: “A rule-based symbolic layout expert” (N. Weste, 1985)

Paper: “Topologizer: An expert system translator of transistor connectivity to symbolic cell layout,” P.W. Kollaritsch, N.H.E. Weste, 1985 IEEE Journal of Solid-State Circuits

Paper: “A unified design representation can work,” P. Kollaritsch, et al., 1989 DAC

Paper: “CLAY: A malleable-cell multi-cell transistor matrix approach for CMOS layout synthesis,” P. Kollaritsch, et al., 1988 ICCAD

Paper: “Circuit optimization techniques in DROID,” H. Chen, P. Kollaritsch, et al., 1991 Int’l Symposium on VLSI Technology, Systems, etc.

Paper: “Area evaluation metrics for transistor placement,” T. Shiple, P. Kollaritsch, et al., 1988 ICCD